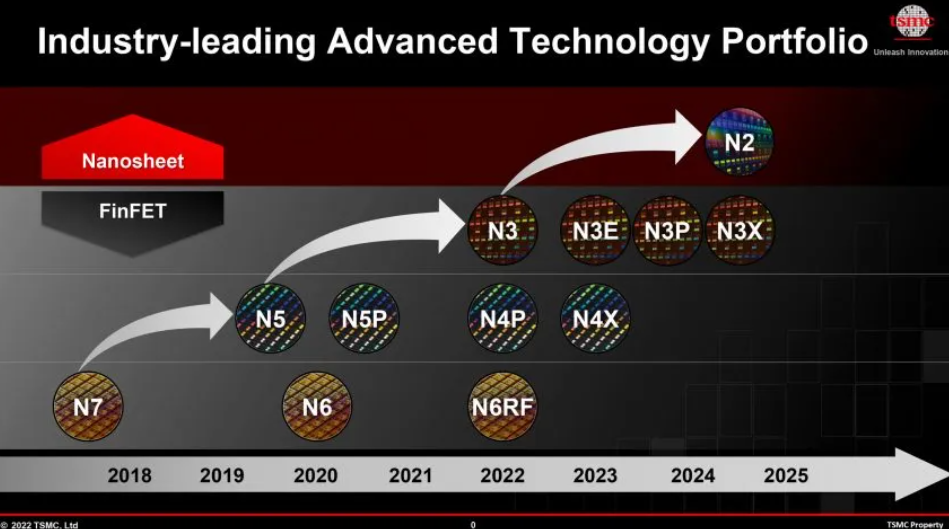

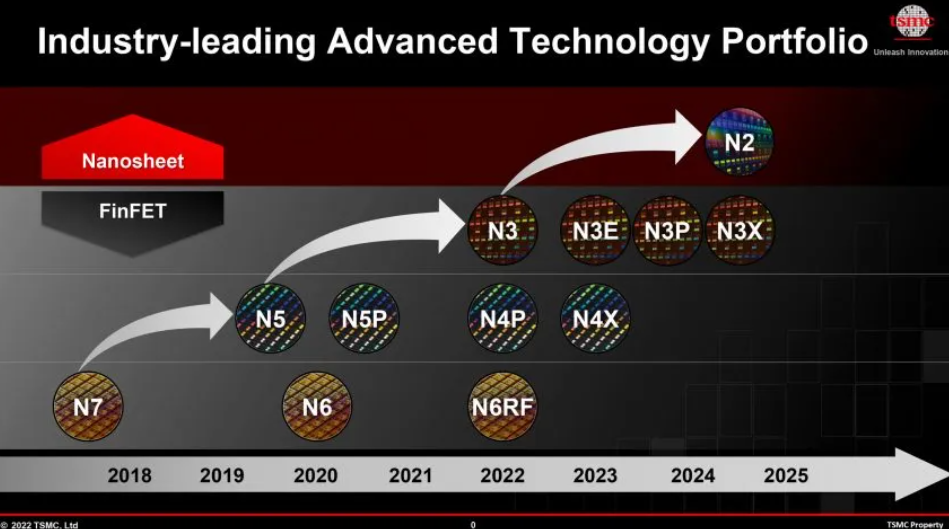

Vn-Z.vn Ngày 18 tháng 06 năm 2022, TSMC vừa giới thiệu thông tin về các quy trình tiên tiến trong tương lai tại hội thảo kỹ thuật năm 2022. Quy trình N3 sẽ được sản xuất hàng loạt vào năm 2022, tiếp theo là quy trình N3E, N3P, N3X, v.v., trong đó quy trình N2 (2nm) sẽ bắt đầu sản xuất hàng loạt vào năm 2025.

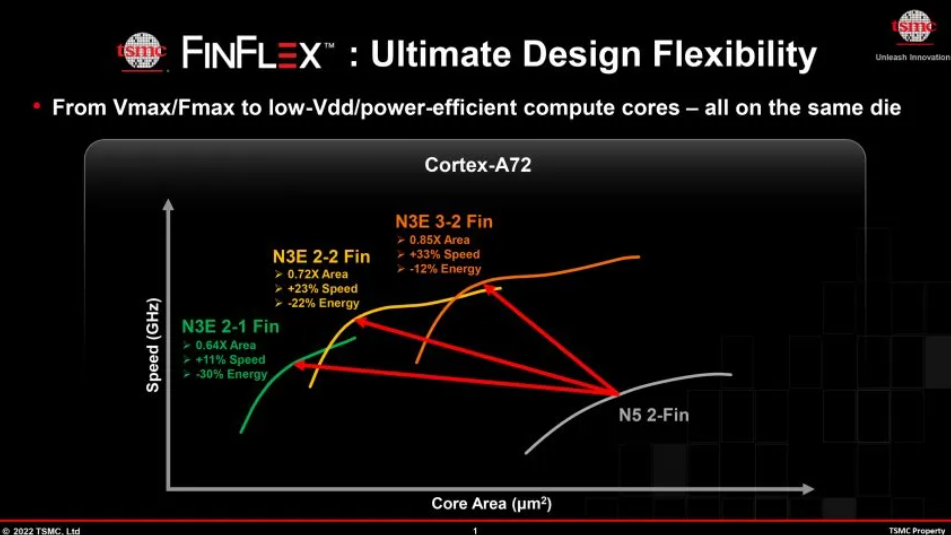

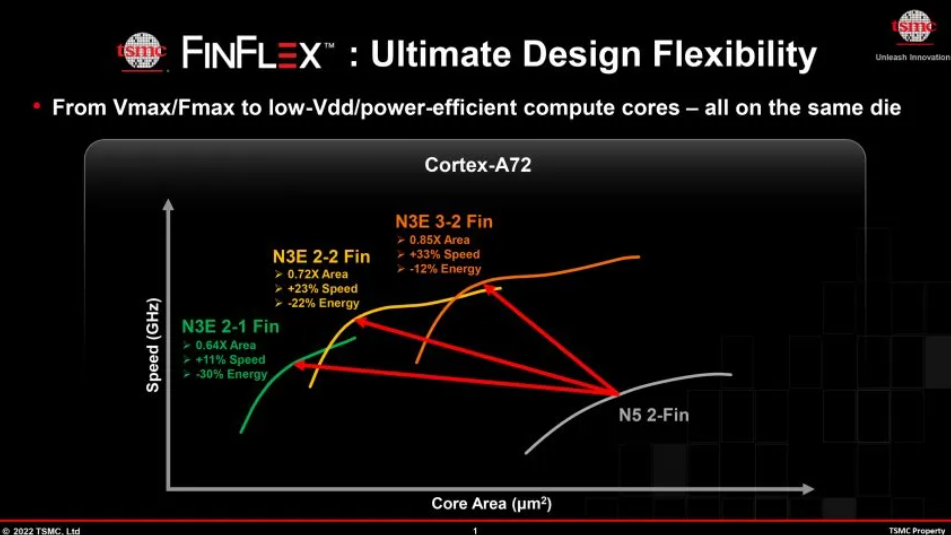

TSMC lần đầu tiên giới thiệu FINFLEX N3, bao gồm các cấu hình 3-2 FIN, 2-2 FIN và 2-1 FIN với các tính năng sau:

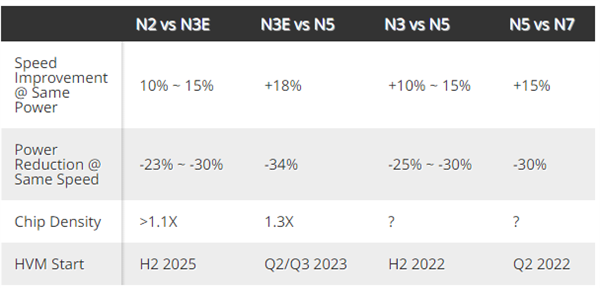

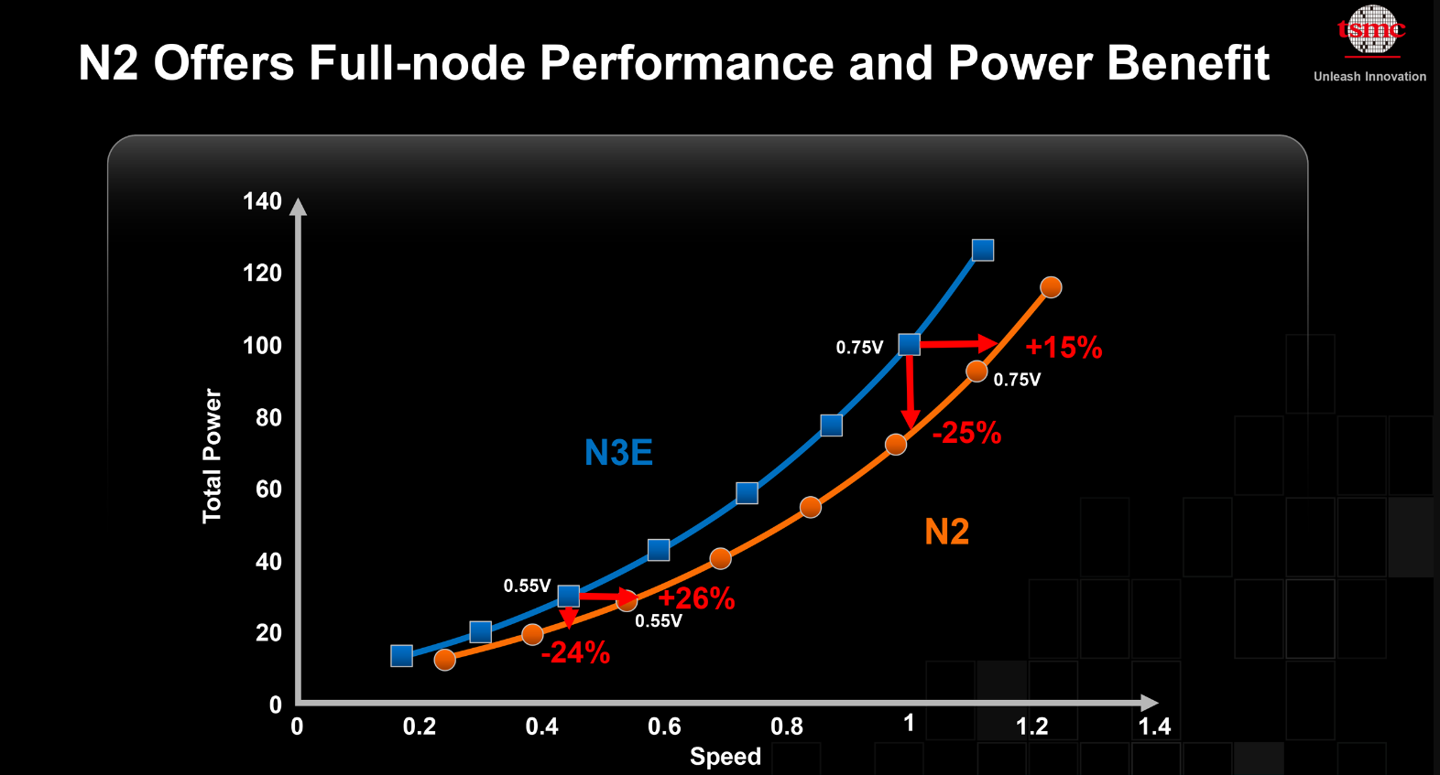

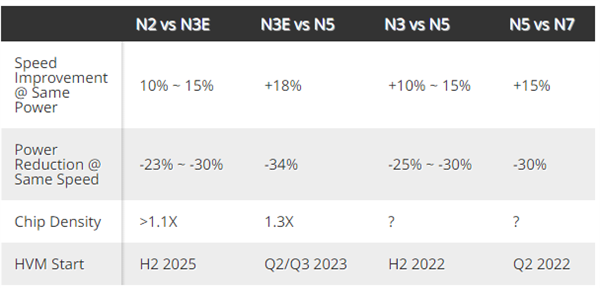

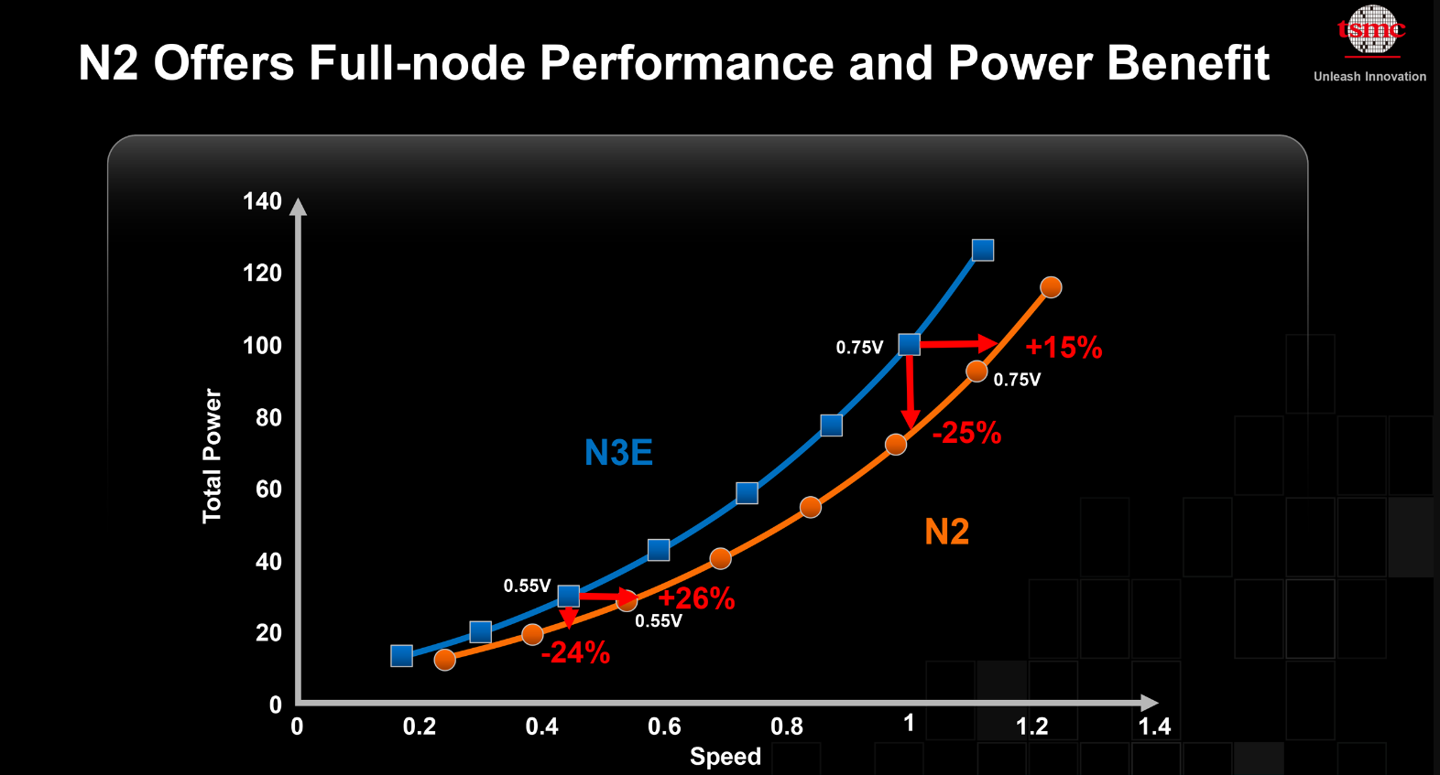

TSMC cho biết N2 là nút đầu tiên của hãng sử dụng bóng bán dẫn toàn cổng (GAAFET) thay vì hiện tại là FinFET (Bóng bán dẫn hiệu ứng trường Fin) . Quy trình sản xuất mới sẽ mang lại hiệu suất toàn diện và lợi thế về điện năng. Trong cùng một mức tiêu thụ điện năng, N2 nhanh hơn 10 ~ 15% so với N3E; trong cùng tốc độ, mức tiêu thụ điện năng giảm 25 ~ 30%. Tuy nhiên, N2 chỉ làm tăng mật độ chết khoảng 10% so với N3E.

Quá trình N2 mang lại hai đổi mới quan trọng: bóng bán dẫn nano (mà TSMC gọi là GAAFETs) và đường ray điện mặt sau. Các bóng bán dẫn nano GAA có các kênh được bao quanh bởi các cổng ở cả bốn phía, giảm rò rỉ. Ngoài ra, các kênh của N2 có thể được mở rộng để tăng dòng điện của ổ đĩa và cải thiện hiệu suất hoặc thu nhỏ để giảm thiểu tiêu thụ điện năng và chi phí. Để cung cấp đủ năng lượng cho các bóng bán dẫn nanô này, TSMC's N2 sử dụng đường ray điện mặt sau, TSMC tin rằng đó là một trong những giải pháp tốt nhất để chống lại lực cản ở đầu cuối dòng (BEOL).

TSMC đang định vị quy trình N2 cho các SoC di động CPU và GPU hiệu suất cao khác nhau,. Hiệu suất cụ thể hiện không được tiết lộ cho đến khi thử nghiệm tiếp theo được phát hành.

Vn-Z.vn team tổng hợp

Sao chép vui lòng ghi rõ nguồn từ Vn-Z.vn

TSMC lần đầu tiên giới thiệu FINFLEX N3, bao gồm các cấu hình 3-2 FIN, 2-2 FIN và 2-1 FIN với các tính năng sau:

- 3-2 FIN - Tần số xung nhịp nhanh nhất và hiệu suất cao nhất cho các nhu cầu tính toán khắt khe nhất

- 2-2 FIN - Hiệu suất hiệu quả, cân bằng tốt giữa hiệu suất năng lượng và mật độ.

- 2-1 FIN - Tiết kiệm năng lượng cực cao, tiêu thụ điện năng thấp nhất, rò rỉ thấp nhất và mật độ cao nhất.

TSMC cho biết N2 là nút đầu tiên của hãng sử dụng bóng bán dẫn toàn cổng (GAAFET) thay vì hiện tại là FinFET (Bóng bán dẫn hiệu ứng trường Fin) . Quy trình sản xuất mới sẽ mang lại hiệu suất toàn diện và lợi thế về điện năng. Trong cùng một mức tiêu thụ điện năng, N2 nhanh hơn 10 ~ 15% so với N3E; trong cùng tốc độ, mức tiêu thụ điện năng giảm 25 ~ 30%. Tuy nhiên, N2 chỉ làm tăng mật độ chết khoảng 10% so với N3E.

Quá trình N2 mang lại hai đổi mới quan trọng: bóng bán dẫn nano (mà TSMC gọi là GAAFETs) và đường ray điện mặt sau. Các bóng bán dẫn nano GAA có các kênh được bao quanh bởi các cổng ở cả bốn phía, giảm rò rỉ. Ngoài ra, các kênh của N2 có thể được mở rộng để tăng dòng điện của ổ đĩa và cải thiện hiệu suất hoặc thu nhỏ để giảm thiểu tiêu thụ điện năng và chi phí. Để cung cấp đủ năng lượng cho các bóng bán dẫn nanô này, TSMC's N2 sử dụng đường ray điện mặt sau, TSMC tin rằng đó là một trong những giải pháp tốt nhất để chống lại lực cản ở đầu cuối dòng (BEOL).

TSMC đang định vị quy trình N2 cho các SoC di động CPU và GPU hiệu suất cao khác nhau,. Hiệu suất cụ thể hiện không được tiết lộ cho đến khi thử nghiệm tiếp theo được phát hành.

Vn-Z.vn team tổng hợp

Sao chép vui lòng ghi rõ nguồn từ Vn-Z.vn