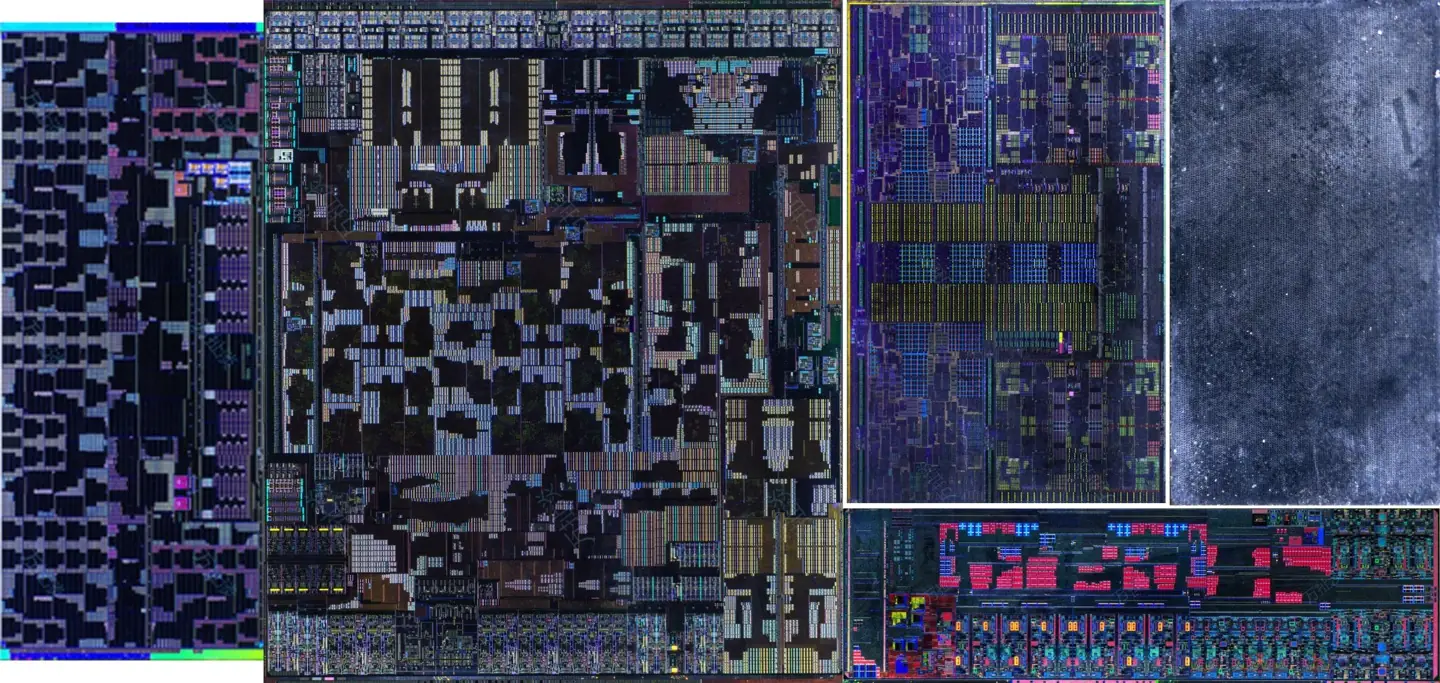

Vn-Z.vn Ngày 22 tháng 12 năm 2023, Ảnh Die Shots thường là hình ảnh microphotography chất lượng cao có thể cho thấy các chi tiết về cấu trúc và bố trí của các thành phần bên trong chip, bao gồm transistor, mạch kết nối và các thành phần khác. Những hình ảnh này có thể hữu ích để phân tích cấu trúc, đánh giá hiệu suất, và nắm bắt thông tin kỹ thuật cụ thể về vi mạch hay CPU.

Theo nguồn thông tin từ HXL (@9559pro) gần đây, tài khoản X này đã đăng dòng tweet chia sẻ hình ảnh Die Shots của vi xử lý Intel Core i Ultra.

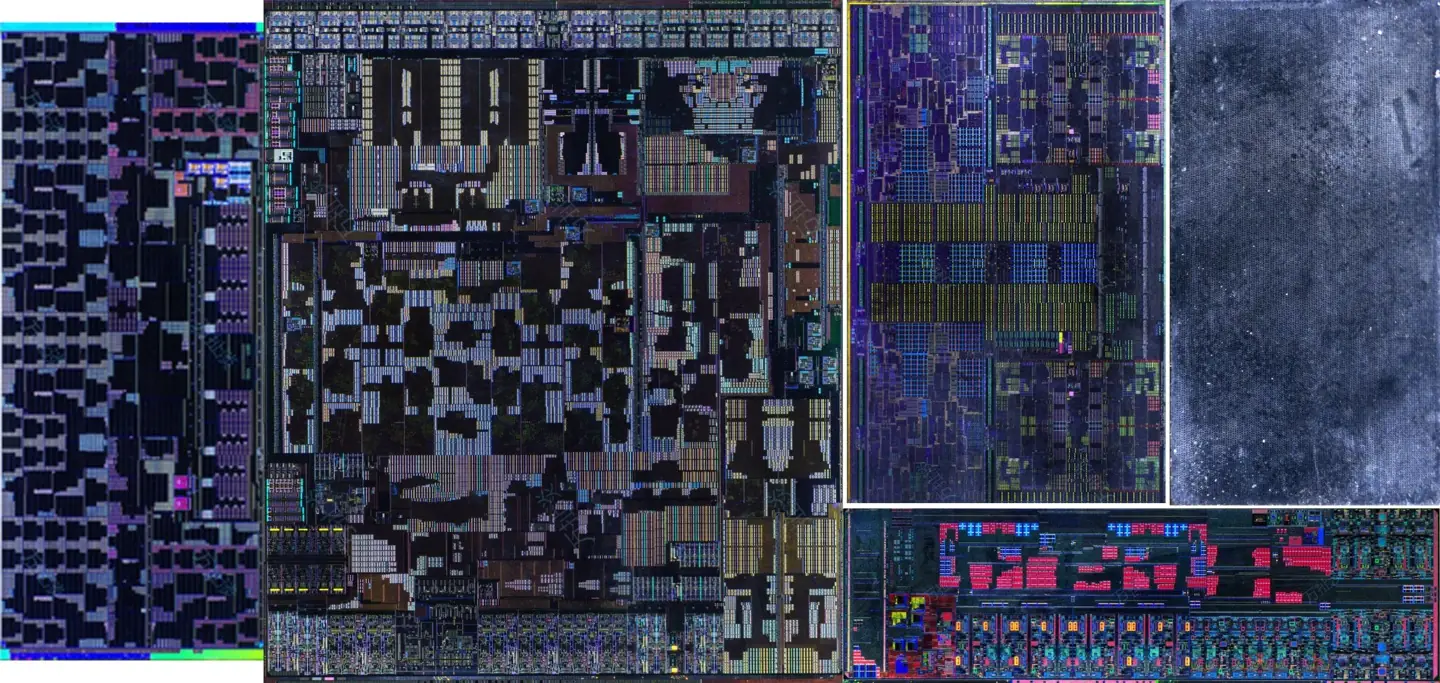

Vi xử lý Intel Core i Ultra 'Meteor Lake' dựa trên kiến trúc phân tách lưu trữ và tính toán (Disaggregated Architecture), thống nhất các IP thông qua hình thức chiplet.

Dựa trên hình ảnh Die Shots đã tiết lộ, vi xử lý Meteor Lake có tổng cộng 4 chiplets, bao gồm tính toán (CPU), đồ họa (GPU), SOC (NPU, vv.) và I / O.

Tất cả 4 tile đều sử dụng công nghệ đóng gói cả bên trong và bên ngoài, điều này có nghĩa là một số tile được Intel đóng gói, trong khi các tile còn lại được các nhà máy wafer bên thứ ba như TSMC đóng gói.

Trong đó, tile CPU chính sử dụng công nghệ đóng gói Intel 4 (7nm) EUV, trong khi SOC Tile và IOE Tile sử dụng công nghệ đóng gói N6 (6nm) của TSMC.

Một thành phần chính khác của vi xử lý Meteor Lake là iGPU (Tiled-GPU), với tên gọi mới là iGPU (Tiled-GPU), sử dụng công nghệ node 5nm của TSMC.

Tôi sẽ giải thích một chút về các Tile kiến trúc của Meteor Lake như sau:

1. Intel Meteor Lake Compute Tile: Đây là trung tâm xử lý, sử dụng công nghệ sản xuất 4 (7nm) EUV của Intel. Nó chịu trách nhiệm xử lý các nhiệm vụ tính toán, có thể bao gồm các lõi chính của bộ vi xử lý và các đơn vị logic.

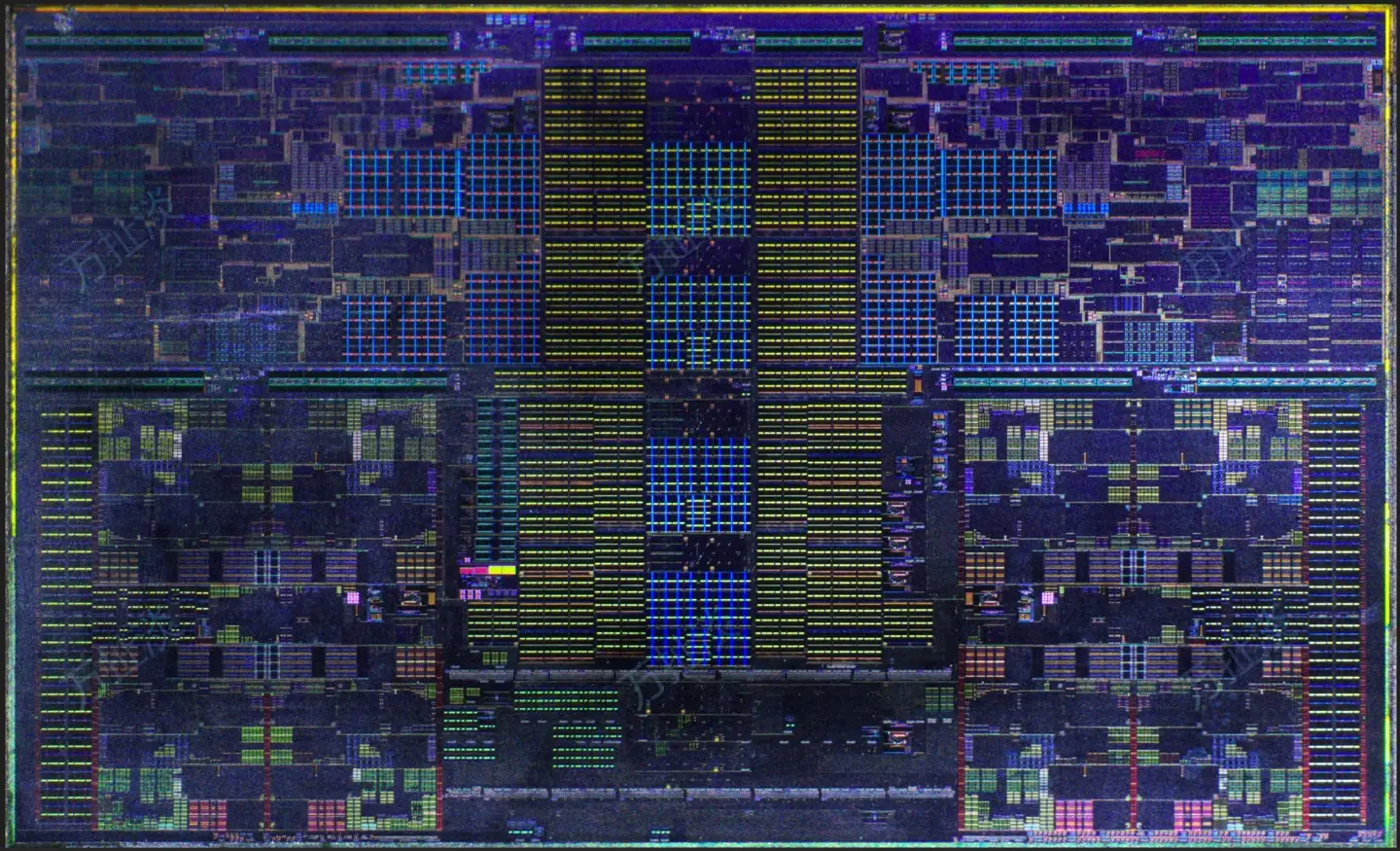

2. Intel Meteor Lake Graphics Tile: Tile này tập trung vào xử lý đồ họa, sử dụng công nghệ 5nm của TSMC. Nó có thể chịu trách nhiệm xử lý hiển thị, kỹ thuật render đồ họa và các nhiệm vụ liên quan đến đồ họa, cung cấp hiệu suất đồ họa tốt hơn.

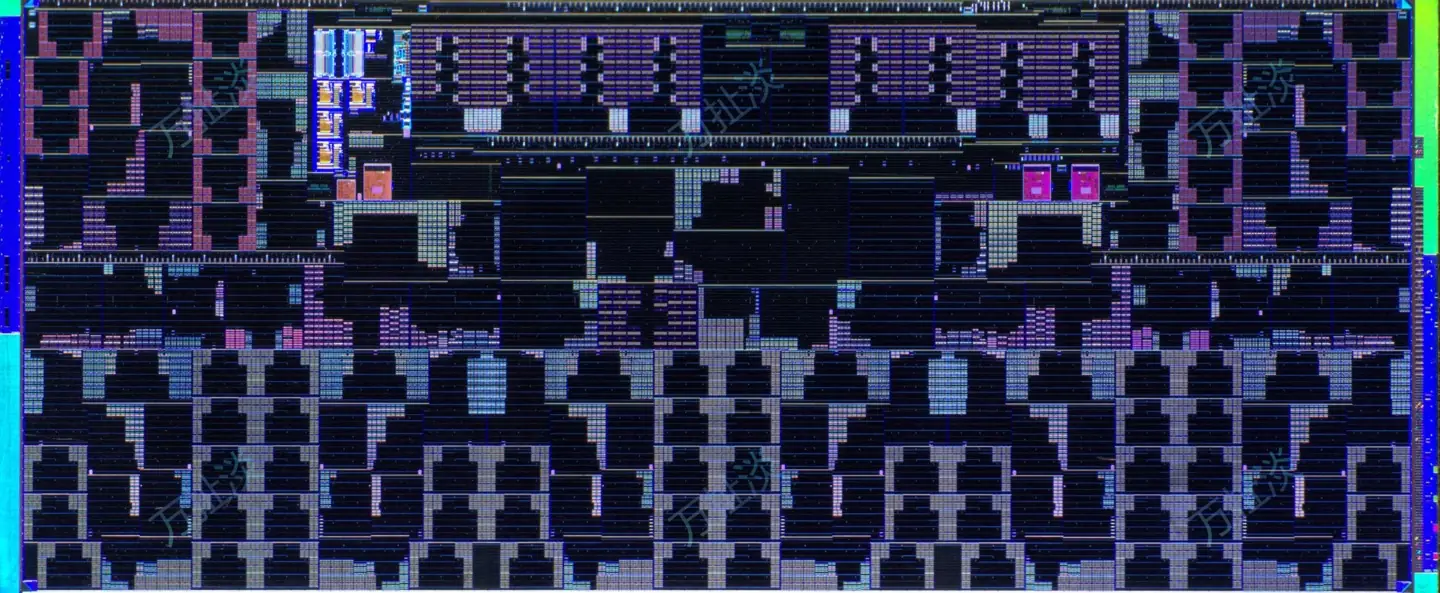

3. ntel Meteor Lake SOC Tile: SOC (chip hệ thống) Tile sử dụng công nghệ 6nm của TSMC. Phần này có thể liên quan đến việc tích hợp cấp hệ thống, bao gồm kết nối, lập lịch và các chức năng khác liên quan đến việc tích hợp hệ thống.

4. Intel Meteor Lake IO Tile: Tile này cũng sử dụng công nghệ 6nm của TSMC, tập trung vào hoạt động đầu vào/ra. Nó có thể chịu trách nhiệm xử lý các kết nối với các thiết bị ngoại vi khác như USB, mạng, lưu trữ và các chức năng liên quan.

Cách tiếp cận này cho phép xử lý hiệu quả các loại nhiệm vụ khác nhau trên các cấu trúc chip khác nhau, cung cấp hiệu suất toàn diện và hiệu quả về năng lượng tốt hơn. Intel dường như đã sử dụng nhiều Tile khác nhau với công nghệ và chức năng khác nhau trong Meteor Lake để tối đa hóa hiệu suất cho từng lĩnh vực cụ thể.

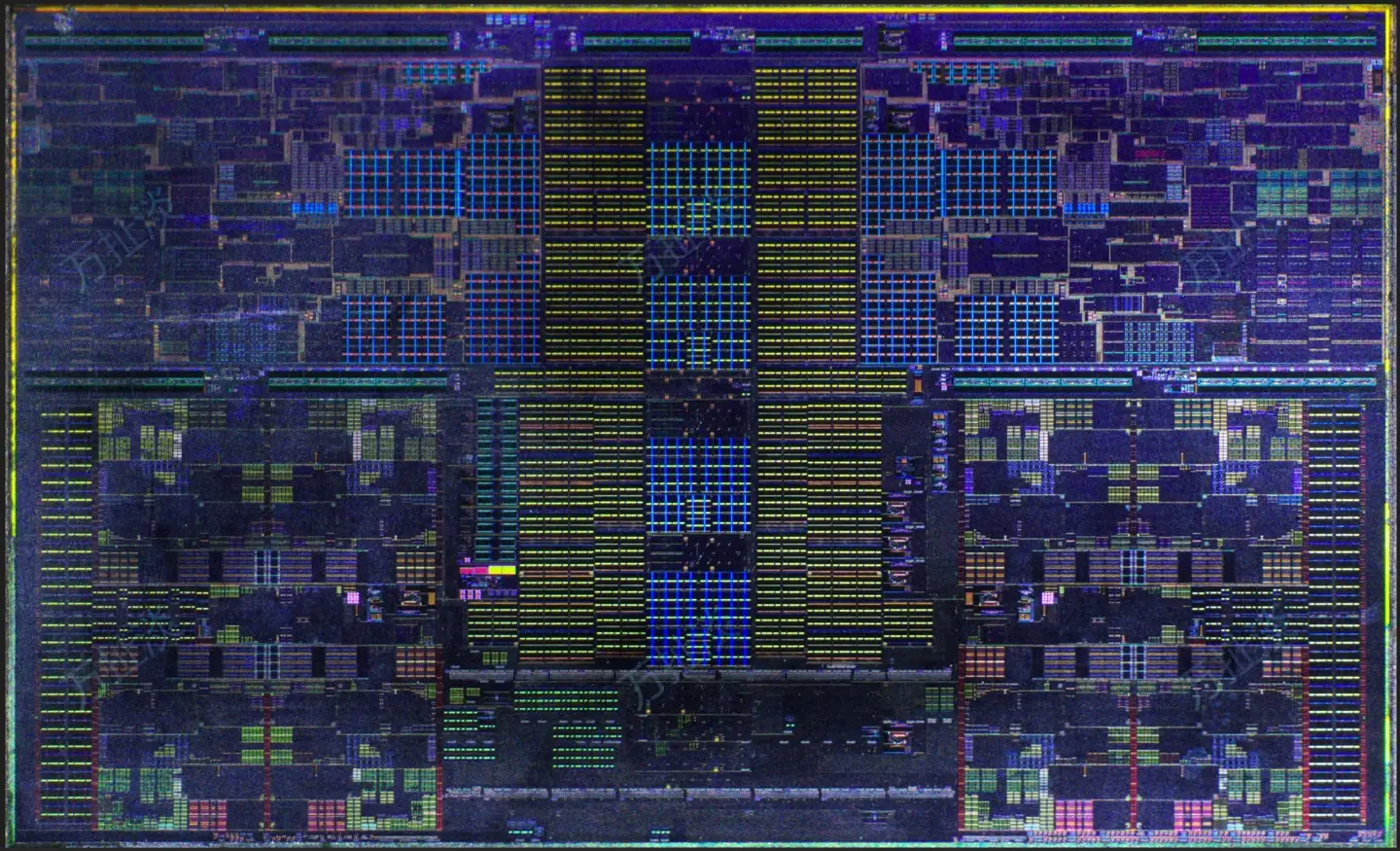

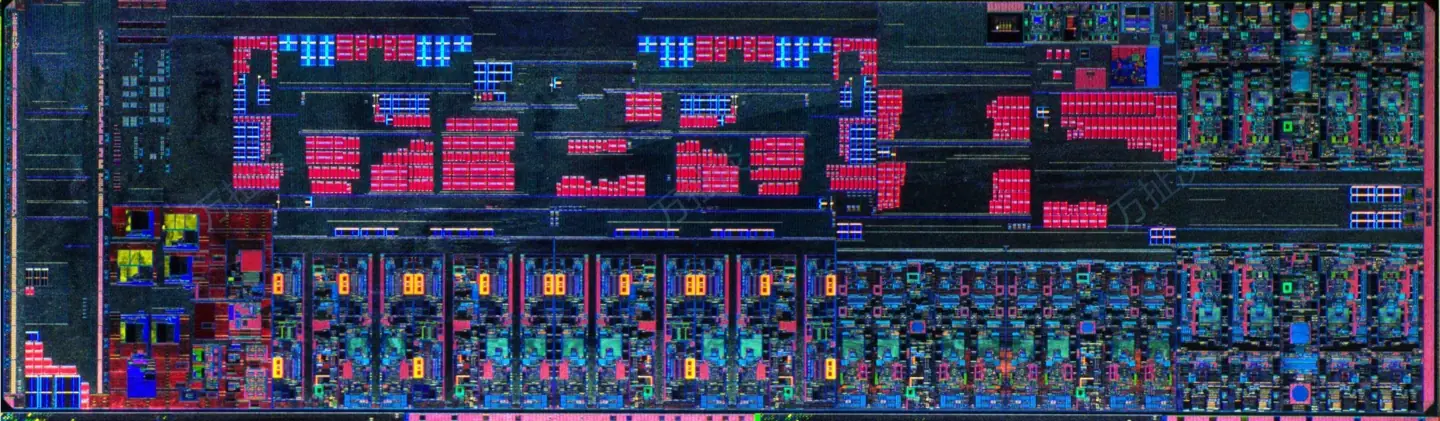

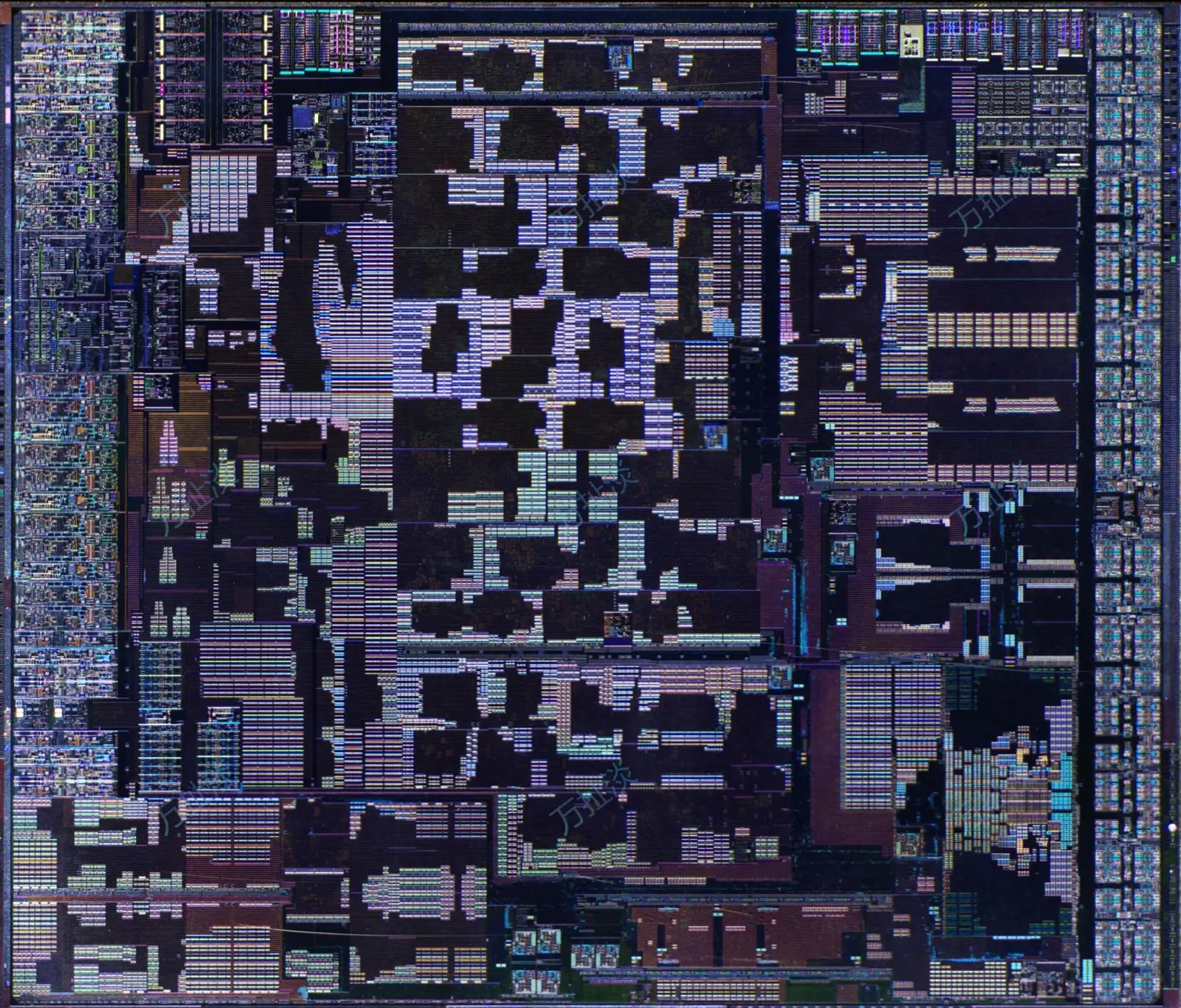

Có thể thấy SKU 2+8+2 trong hình ảnh Die Shot này, bao gồm:

- 2 lõi P dựa trên Redwood Cove

- 8 lõi E dựa trên Crestmont

- 2 lõi E tiêu thụ điện năng thấp dựa trên cùng một Crestmont

2 lõi P và 8 lõi E đầu tiên nằm trong Ô Điện toán (CPU), bạn có thể thấy hai lõi P lớn ở trên cùng và sau đó là 8 lõi E nhỏ hơn ở phía dưới.

Intel Meteor Lake Compute CPU Tile

Phần lớn ở giữa là bộ đệm. Trong cấu hình này, có tổng cộng 12 MB bộ đệm thông minh, trong đó Redwood Cove P-Core có 2 MB L2 mỗi lõi và Crestmont E-Core chứa 4 MB bộ đệm L2 trên mỗi cụm.

Intel Meteor Lake Compute CPU Tile

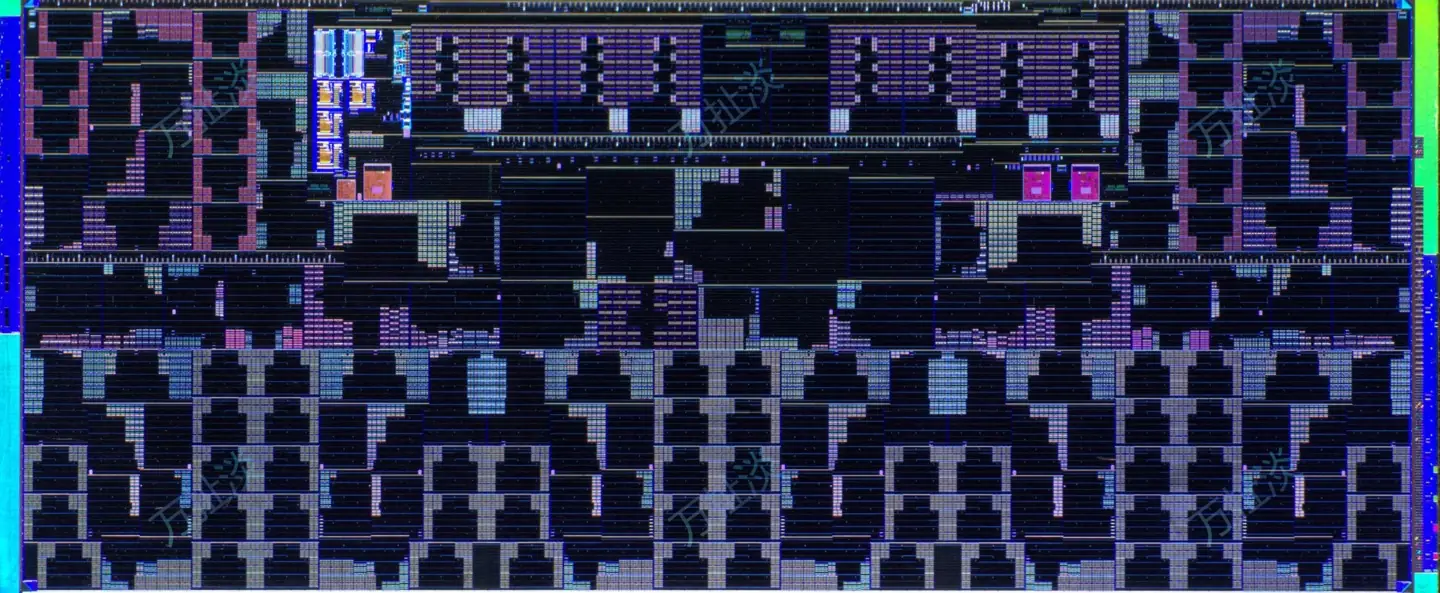

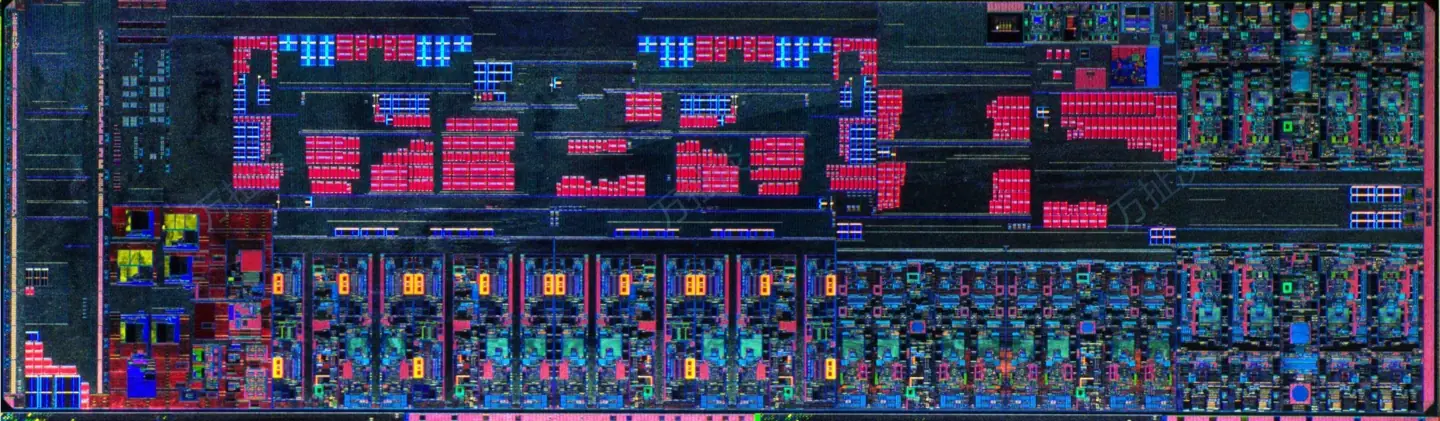

Trên GPU Tile, có thể thấy 4 phiên bản Xe-Core dựa trên kiến trúc Arc Akchemist và các bộ phận đông đúc nhất dường như là các mô-đun SOC và I/O, có nhiều bộ phận khác nhau như bộ điều khiển (bộ nhớ/bộ lưu trữ/PCIe) , NPU, đảo video chuyên dụng tiêu thụ điện năng thấp và hơn thế nữa.

Meteor Lake SOC Tile

SOC Tile có hai lõi Crestmont LP E.

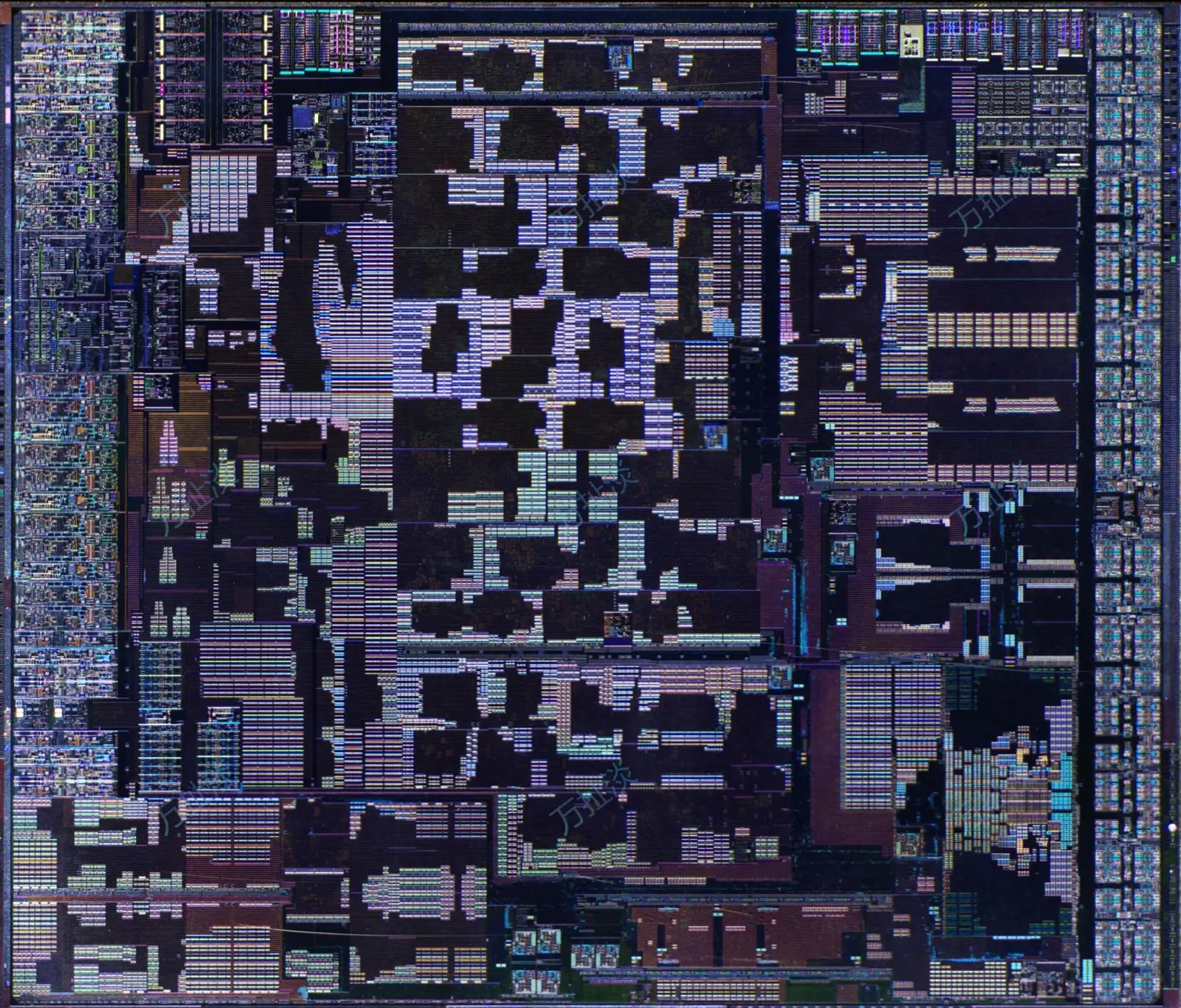

Meteor Lake IOE Tile

Các nhân E LP (Low Power) trên SOC Tile thường được thiết kế để tiết kiệm năng lượng hơn so với các nhân thông thường. Chúng có thể được sử dụng trong các trường hợp đòi hỏi hiệu suất tiêu thụ năng lượng thấp hơn, chẳng hạn như trong các thiết bị di động, các thiết bị IoT, hoặc trong các tác vụ ít yêu cầu điện năng. Việc tích hợp những nhân này vào SOC Tile giúp cải thiện hiệu suất năng lượng và cung cấp sự linh hoạt trong việc sử dụng cho các ứng dụng yêu cầu sự tiết kiệm điện năng.

Theo nguồn thông tin từ HXL (@9559pro) gần đây, tài khoản X này đã đăng dòng tweet chia sẻ hình ảnh Die Shots của vi xử lý Intel Core i Ultra.

Vi xử lý Intel Core i Ultra 'Meteor Lake' dựa trên kiến trúc phân tách lưu trữ và tính toán (Disaggregated Architecture), thống nhất các IP thông qua hình thức chiplet.

Dựa trên hình ảnh Die Shots đã tiết lộ, vi xử lý Meteor Lake có tổng cộng 4 chiplets, bao gồm tính toán (CPU), đồ họa (GPU), SOC (NPU, vv.) và I / O.

Tất cả 4 tile đều sử dụng công nghệ đóng gói cả bên trong và bên ngoài, điều này có nghĩa là một số tile được Intel đóng gói, trong khi các tile còn lại được các nhà máy wafer bên thứ ba như TSMC đóng gói.

Trong đó, tile CPU chính sử dụng công nghệ đóng gói Intel 4 (7nm) EUV, trong khi SOC Tile và IOE Tile sử dụng công nghệ đóng gói N6 (6nm) của TSMC.

Một thành phần chính khác của vi xử lý Meteor Lake là iGPU (Tiled-GPU), với tên gọi mới là iGPU (Tiled-GPU), sử dụng công nghệ node 5nm của TSMC.

Tôi sẽ giải thích một chút về các Tile kiến trúc của Meteor Lake như sau:

1. Intel Meteor Lake Compute Tile: Đây là trung tâm xử lý, sử dụng công nghệ sản xuất 4 (7nm) EUV của Intel. Nó chịu trách nhiệm xử lý các nhiệm vụ tính toán, có thể bao gồm các lõi chính của bộ vi xử lý và các đơn vị logic.

2. Intel Meteor Lake Graphics Tile: Tile này tập trung vào xử lý đồ họa, sử dụng công nghệ 5nm của TSMC. Nó có thể chịu trách nhiệm xử lý hiển thị, kỹ thuật render đồ họa và các nhiệm vụ liên quan đến đồ họa, cung cấp hiệu suất đồ họa tốt hơn.

3. ntel Meteor Lake SOC Tile: SOC (chip hệ thống) Tile sử dụng công nghệ 6nm của TSMC. Phần này có thể liên quan đến việc tích hợp cấp hệ thống, bao gồm kết nối, lập lịch và các chức năng khác liên quan đến việc tích hợp hệ thống.

4. Intel Meteor Lake IO Tile: Tile này cũng sử dụng công nghệ 6nm của TSMC, tập trung vào hoạt động đầu vào/ra. Nó có thể chịu trách nhiệm xử lý các kết nối với các thiết bị ngoại vi khác như USB, mạng, lưu trữ và các chức năng liên quan.

Cách tiếp cận này cho phép xử lý hiệu quả các loại nhiệm vụ khác nhau trên các cấu trúc chip khác nhau, cung cấp hiệu suất toàn diện và hiệu quả về năng lượng tốt hơn. Intel dường như đã sử dụng nhiều Tile khác nhau với công nghệ và chức năng khác nhau trong Meteor Lake để tối đa hóa hiệu suất cho từng lĩnh vực cụ thể.

Có thể thấy SKU 2+8+2 trong hình ảnh Die Shot này, bao gồm:

- 2 lõi P dựa trên Redwood Cove

- 8 lõi E dựa trên Crestmont

- 2 lõi E tiêu thụ điện năng thấp dựa trên cùng một Crestmont

2 lõi P và 8 lõi E đầu tiên nằm trong Ô Điện toán (CPU), bạn có thể thấy hai lõi P lớn ở trên cùng và sau đó là 8 lõi E nhỏ hơn ở phía dưới.

Intel Meteor Lake Compute CPU Tile

Phần lớn ở giữa là bộ đệm. Trong cấu hình này, có tổng cộng 12 MB bộ đệm thông minh, trong đó Redwood Cove P-Core có 2 MB L2 mỗi lõi và Crestmont E-Core chứa 4 MB bộ đệm L2 trên mỗi cụm.

Intel Meteor Lake Compute CPU Tile

Meteor Lake SOC Tile

Meteor Lake IOE Tile

BÀI MỚI ĐANG THẢO LUẬN