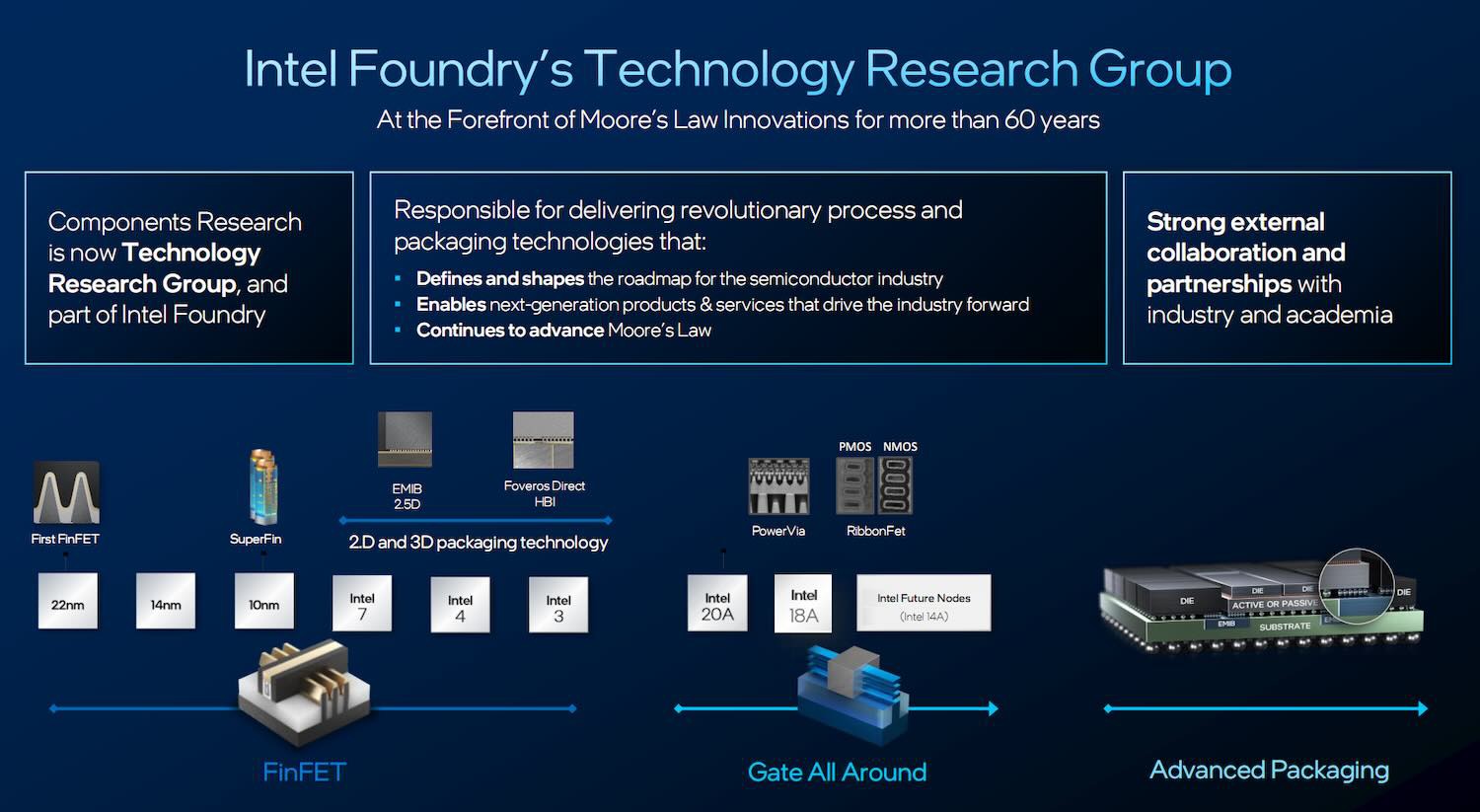

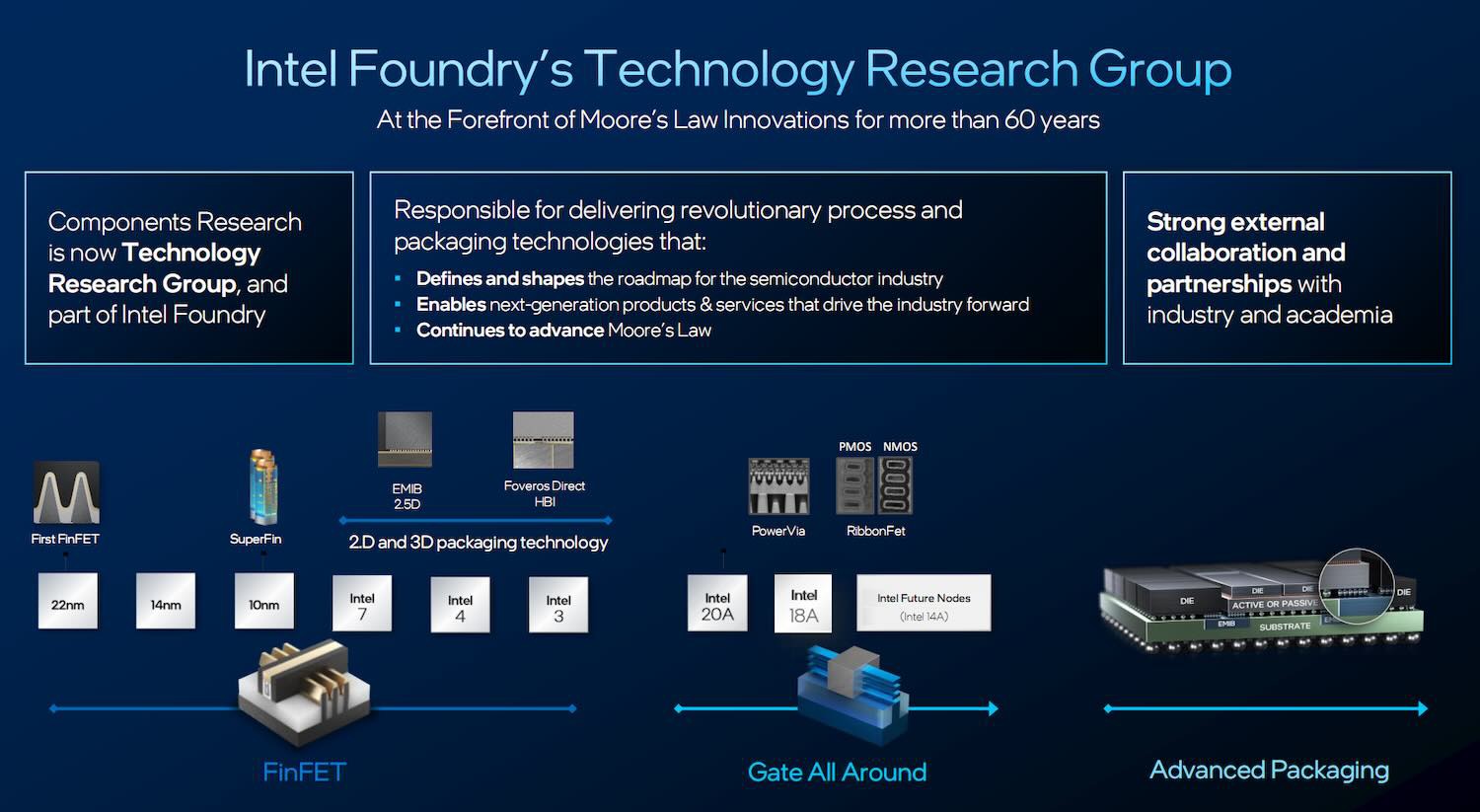

Vn-Z.vn Ngày 09 tháng 12 năm 2024, Tại Hội nghị Thiết bị Điện tử Quốc tế IEEE IEDM 2024, Intel Foundry đã trình bày bốn đột phá lớn trong công nghệ quy trình bán dẫn, bao gồm vật liệu mới, đóng gói dị thể, công nghệ toàn cổng bao (GAA), và các giải pháp khác.

Hiện tại, Intel đang thực hiện kế hoạch đạt 5 nút quy trình trong 4 năm, với mục tiêu đến năm 2030 đóng gói 1 nghìn tỷ bóng bán dẫn trên một chip duy nhất. Các công nghệ tiên tiến về bóng bán dẫn, thu nhỏ, kết nối liên chip và đóng gói là những yếu tố thiết yếu. Dưới đây là chi tiết về bốn đột phá này:

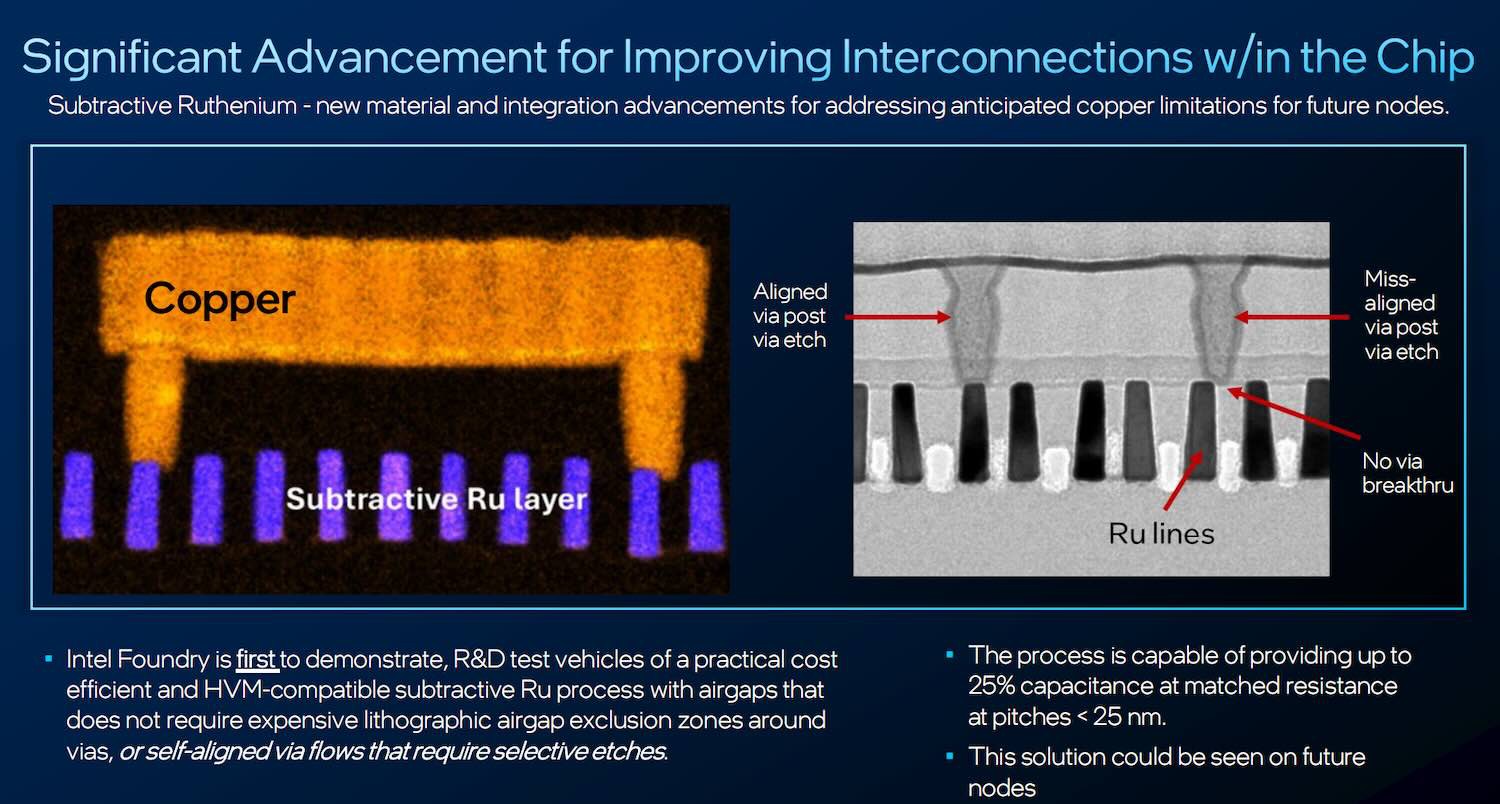

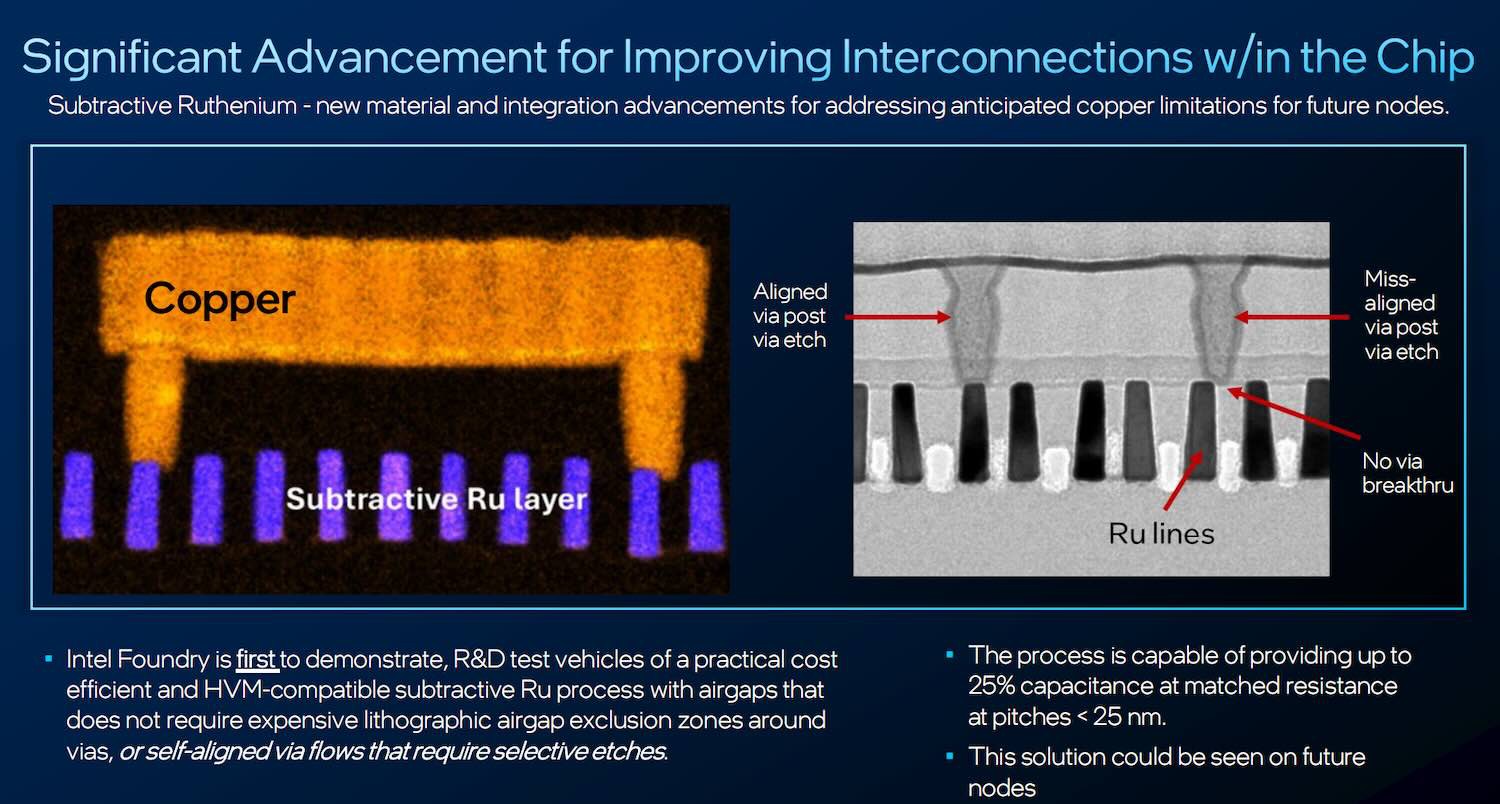

1. Công nghệ liên kết điện giảm dần với Ruteni

• Sử dụng ruteni, một vật liệu kim loại mới, kết hợp với công nghệ màng mỏng và khe khí (airgap), Intel đã đạt tiến bộ lớn trong việc thu nhỏ liên kết, đảm bảo khả năng sản xuất hàng loạt với chi phí hiệu quả.

• Khe khí cho phép giảm độ phức tạp của quy trình mà không cần các khu vực quang khắc tốn kém hoặc sử dụng kỹ thuật ăn mòn tự căn chỉnh.

• Ở mật độ liên kết dưới 25 nm, công nghệ này có thể giảm đến 25% điện dung giữa các đường dẫn, tạo lợi thế vượt trội so với công nghệ liên kết đồng truyền thống.

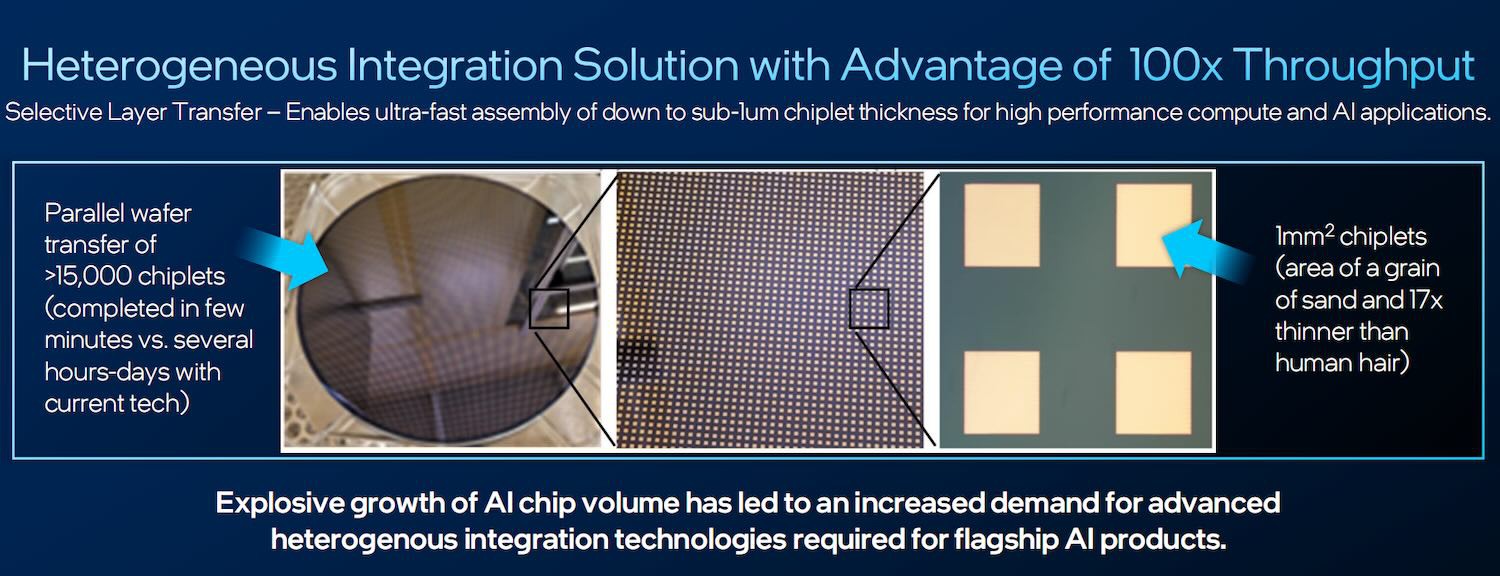

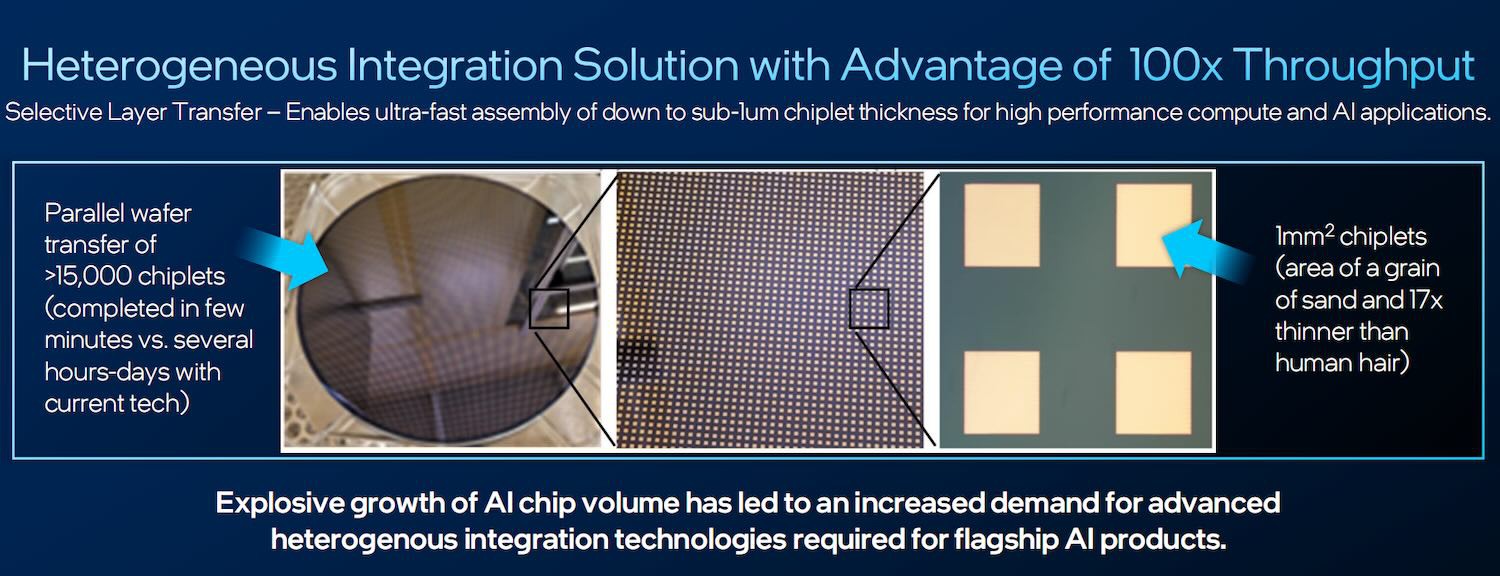

2. Chuyển giao lớp chọn lọc (SLT)

• Đây là giải pháp tích hợp dị thể với khả năng đóng gói các chiplet siêu mỏng linh hoạt hơn. So với công nghệ kết nối chip-to-wafer truyền thống, SLT giúp giảm kích thước chip và nâng cao tỉ lệ hình học, đồng thời cải thiện thông lượng đóng gói gấp 100 lần.

• Kỹ thuật này cũng mang lại mật độ chức năng cao hơn, kết hợp với công nghệ liên kết lai hoặc liên kết hợp nhất để tích hợp chiplet từ các tấm wafer khác nhau.

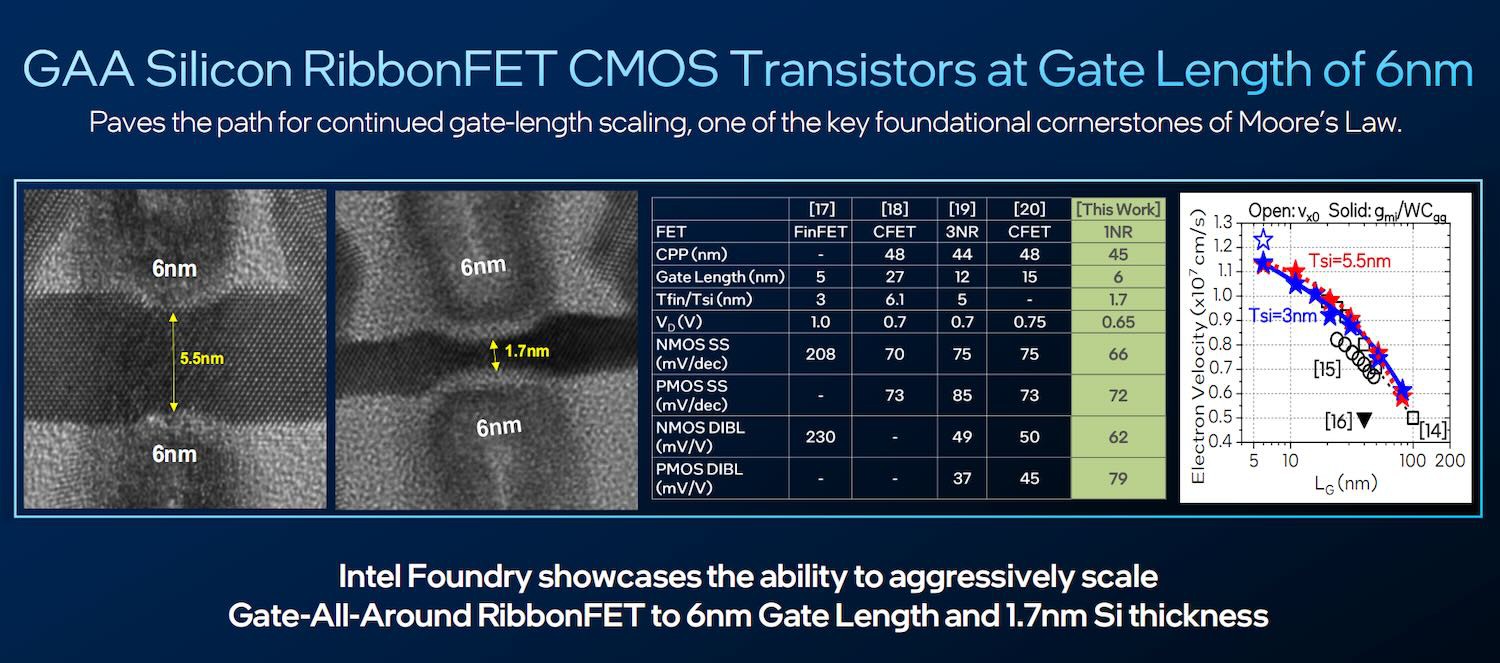

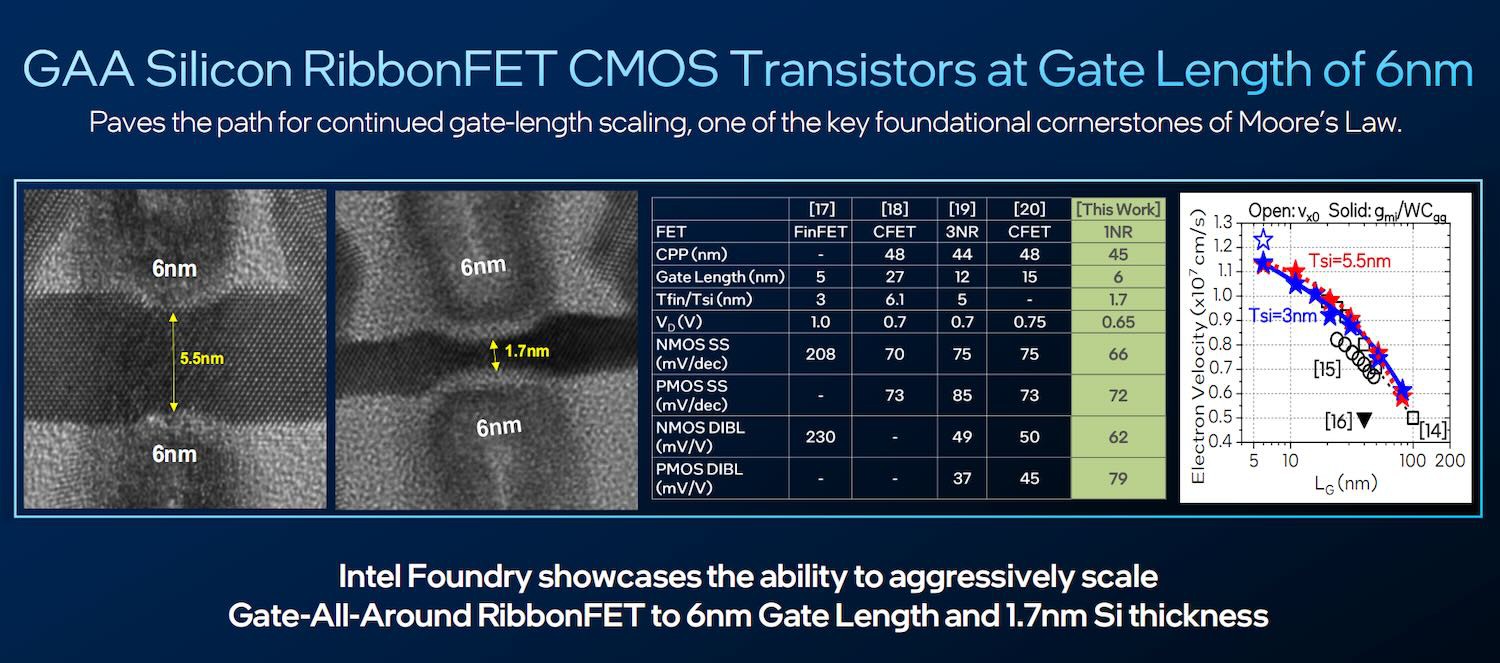

3. Bóng bán dẫn RibbonFET CMOS trên nền silicon

• Intel đã trình diễn bóng bán dẫn RibbonFET GAA với chiều dài cổng chỉ 6 nm, đặt tiêu chuẩn mới về hiệu suất và kiểm soát hiệu ứng kênh ngắn.

• Thiết kế này mở đường cho việc thu nhỏ thêm chiều dài cổng, một yếu tố then chốt để duy trì định luật Moore.

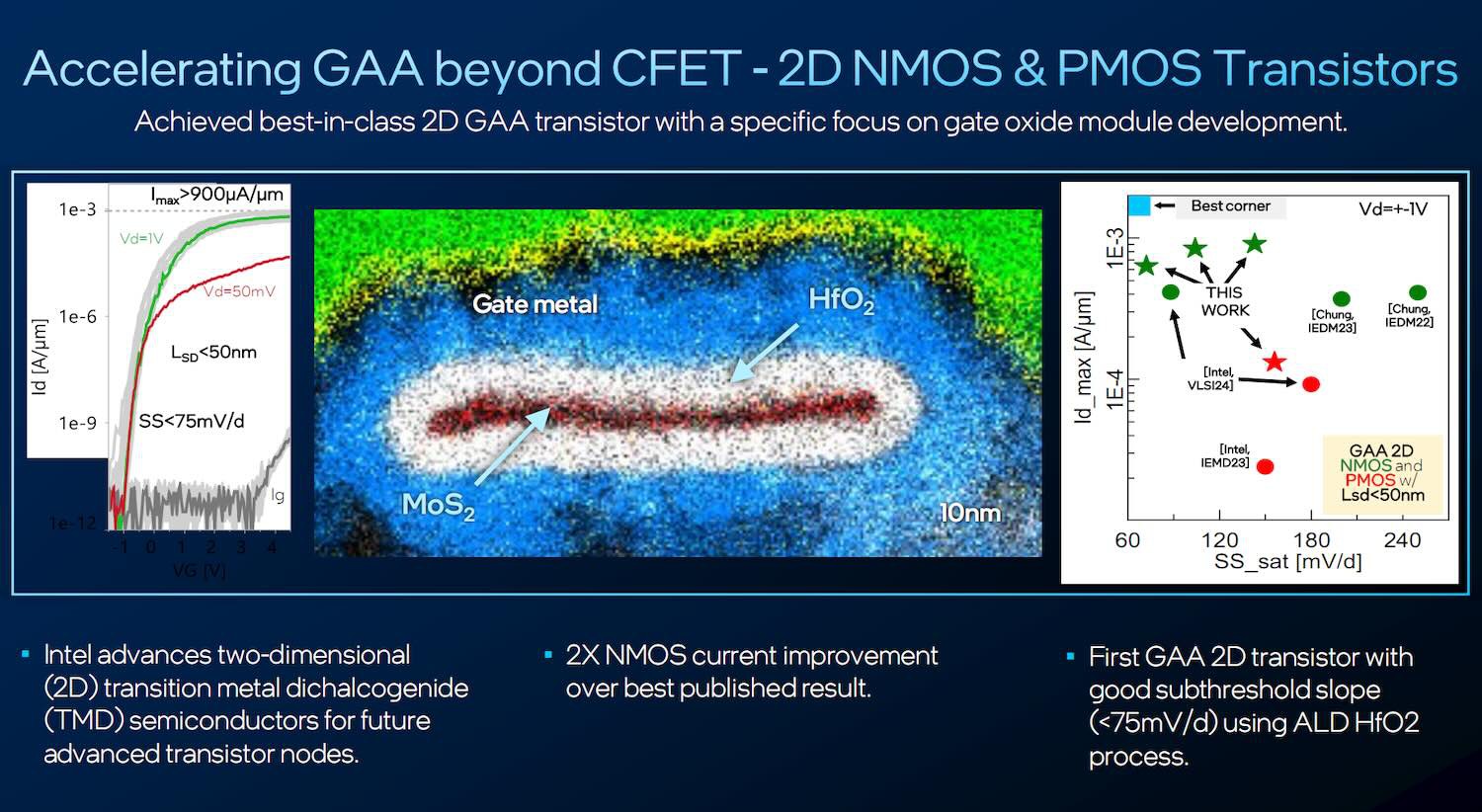

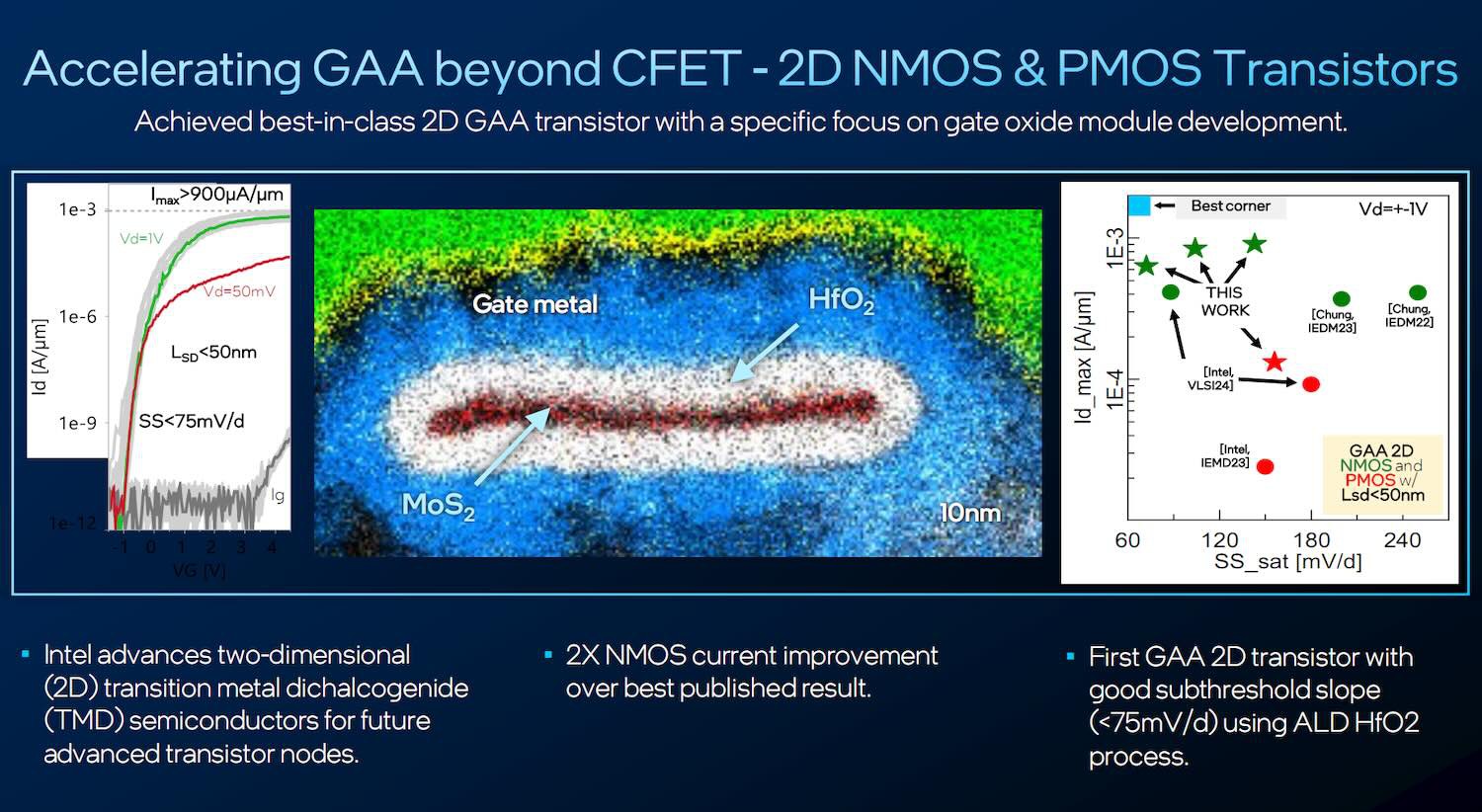

4. Lớp oxit cổng 2D cho bóng bán dẫn GAA

• Để đẩy mạnh đổi mới trong công nghệ GAA ngoài CFET, Intel đã nghiên cứu sản xuất bóng bán dẫn GAA 2D cho NMOS và PMOS với chiều dài cổng chỉ 30 nm.

• Kết hợp với nghiên cứu về 2D TMD (hợp chất disulfide kim loại chuyển tiếp), công nghệ này có thể thay thế silicon trong các quy trình tiên tiến.

Nghiên cứu về GaN trên TRSOI

Ngoài 4 đột phá kể trên, Intel Foundry cũng đang nghiên cứu vật liệu GaN (Gallium Nitride) trên nền silicon TRSOI (Trap-Rich Silicon-On-Insulator). Công nghệ này giúp giảm tổn thất tín hiệu, cải thiện độ tuyến tính và mở ra tiềm năng tích hợp tiên tiến từ mặt sau của tấm nền.

Những cải tiến này sẽ đóng góp quan trọng trong việc thu nhỏ và nâng cao hiệu suất chip, đồng thời củng cố vị thế của Intel trong ngành công nghiệp bán dẫn toàn cầu.

Hiện tại, Intel đang thực hiện kế hoạch đạt 5 nút quy trình trong 4 năm, với mục tiêu đến năm 2030 đóng gói 1 nghìn tỷ bóng bán dẫn trên một chip duy nhất. Các công nghệ tiên tiến về bóng bán dẫn, thu nhỏ, kết nối liên chip và đóng gói là những yếu tố thiết yếu. Dưới đây là chi tiết về bốn đột phá này:

1. Công nghệ liên kết điện giảm dần với Ruteni

• Khe khí cho phép giảm độ phức tạp của quy trình mà không cần các khu vực quang khắc tốn kém hoặc sử dụng kỹ thuật ăn mòn tự căn chỉnh.

• Ở mật độ liên kết dưới 25 nm, công nghệ này có thể giảm đến 25% điện dung giữa các đường dẫn, tạo lợi thế vượt trội so với công nghệ liên kết đồng truyền thống.

2. Chuyển giao lớp chọn lọc (SLT)

• Kỹ thuật này cũng mang lại mật độ chức năng cao hơn, kết hợp với công nghệ liên kết lai hoặc liên kết hợp nhất để tích hợp chiplet từ các tấm wafer khác nhau.

3. Bóng bán dẫn RibbonFET CMOS trên nền silicon

• Thiết kế này mở đường cho việc thu nhỏ thêm chiều dài cổng, một yếu tố then chốt để duy trì định luật Moore.

4. Lớp oxit cổng 2D cho bóng bán dẫn GAA

• Kết hợp với nghiên cứu về 2D TMD (hợp chất disulfide kim loại chuyển tiếp), công nghệ này có thể thay thế silicon trong các quy trình tiên tiến.

Nghiên cứu về GaN trên TRSOI

Ngoài 4 đột phá kể trên, Intel Foundry cũng đang nghiên cứu vật liệu GaN (Gallium Nitride) trên nền silicon TRSOI (Trap-Rich Silicon-On-Insulator). Công nghệ này giúp giảm tổn thất tín hiệu, cải thiện độ tuyến tính và mở ra tiềm năng tích hợp tiên tiến từ mặt sau của tấm nền.

BÀI MỚI ĐANG THẢO LUẬN