Tổ chức JEDEC đang gấp rút xây dựng tiêu chuẩn bộ nhớ mới mang tên SPHBM4 (Standard Package High Bandwidth Memory thế hệ thứ tư). Chỉ với độ rộng bus 512-bit, SPHBM4 đã có thể đạt được mức băng thông tương đương HBM4, đồng thời vẫn tương thích với đế hữu cơ truyền thống, qua đó mang lại dung lượng lớn hơn và chi phí tích hợp thấp hơn.

Có thể xem SPHBM4 là một dạng bộ nhớ nằm giữa DDR truyền thống và HBM thế hệ mới, nhằm lấp đầy khoảng trống mà HBM chưa bao phủ ở nhiều phân khúc thị trường. Tuy nhiên, SPHBM4 không được thiết kế để dùng cho card đồ họa và cũng không nhằm thay thế bộ nhớ đồ họa GDDR.

HBM thông thường sử dụng độ rộng bus 1024-bit hoặc 2048-bit, nhờ đó đạt hiệu năng, băng thông và hiệu suất năng lượng gần như không đối thủ. Nhưng độ rộng bus cực lớn này cũng chiếm rất nhiều diện tích chip quý giá, không chỉ hạn chế số lượng chip xếp chồng và dung lượng đóng gói, mà còn tiếp tục kìm hãm hiệu năng của từng card tăng tốc AI đơn lẻ cũng như tổng sức mạnh tính toán của cả cụm hệ thống.

SPHBM4 áp dụng công nghệ truyền nối tiếp 4:1, giúp giảm độ rộng bus từ 2048-bit xuống còn 512-bit nhưng vẫn giữ nguyên mức băng thông, và dĩ nhiên vẫn vượt xa DDR5.

Tuy vậy, JEDEC chưa công bố rõ ràng liệu điều này có đạt được bằng cách tăng tốc độ truyền dữ liệu lên gấp 4 lần (32 GT/s) hay thông qua một cơ chế mã hóa mới với tần số cao hơn.

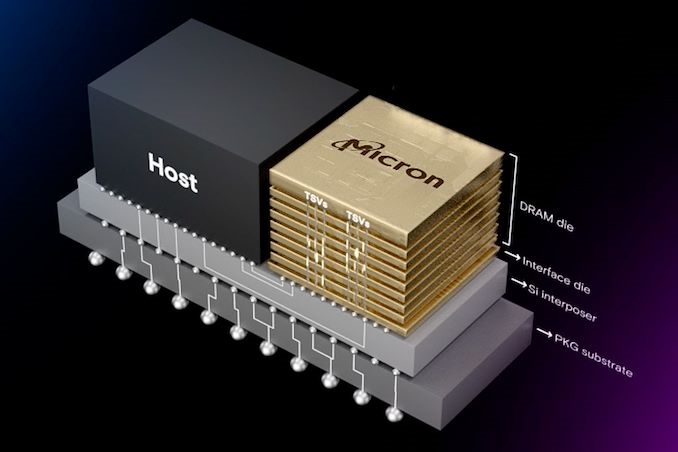

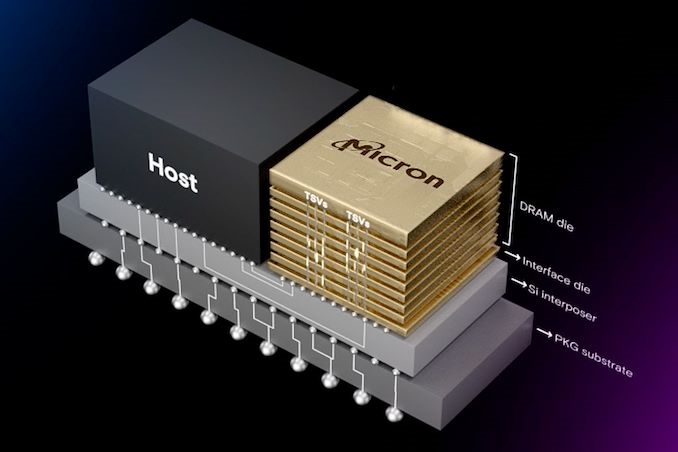

Bên trong gói SPHBM4 sử dụng die nền tiêu chuẩn của ngành cùng die HBM4, qua đó đảm bảo dung lượng của mỗi khối xếp chồng ngang bằng HBM4 hoặc HBM4E, tối đa có thể đạt 64 GB. Thiết kế này cũng giúp đơn giản hóa bộ điều khiển, cấu trúc đóng gói tổng thể và giảm chi phí.

Về mặt lý thuyết, dung lượng của SPHBM4 thậm chí còn có thể cao hơn, gấp bốn lần HBM4. Điều này khiến nhiều người liên tưởng đến thời kỳ HBM từng được dùng làm bộ nhớ đồ họa, và đặt câu hỏi liệu SPHBM4 có thể trở thành chuẩn VRAM mới hay không.

Câu trả lời rõ ràng là không.

Nguyên nhân là vì mục tiêu thiết kế cốt lõi của SPHBM4 là đạt băng thông cấp HBM4, đảm bảo hiệu năng và dung lượng, chứ không phải tối ưu chi phí và điện năng tiêu thụ.

Chi phí của SPHBM4 chắc chắn thấp hơn HBM4 và HBM4E, đặc biệt nhờ không cần sử dụng interposer đắt đỏ, nhưng bản thân nó vẫn là thiết kế bộ nhớ xếp chồng, nên tất yếu đắt hơn nhiều so với chip DRAM thông thường.

Bên cạnh đó, SPHBM4 còn yêu cầu giao diện nền mạch chuyên dụng, công nghệ TSV (lỗ xuyên silicon) và các kỹ thuật đóng gói tích hợp tiên tiến, khiến chi phí khó có thể hạ xuống mức của GDDR.

Vì vậy, trong card đồ họa, việc dùng một chip SPHBM4 để thay thế nhiều chip GDDR6/7 không những tốn kém hơn, mà mức cải thiện hiệu năng mang lại cũng không thực sự đáng kể.

Có thể xem SPHBM4 là một dạng bộ nhớ nằm giữa DDR truyền thống và HBM thế hệ mới, nhằm lấp đầy khoảng trống mà HBM chưa bao phủ ở nhiều phân khúc thị trường. Tuy nhiên, SPHBM4 không được thiết kế để dùng cho card đồ họa và cũng không nhằm thay thế bộ nhớ đồ họa GDDR.

HBM thông thường sử dụng độ rộng bus 1024-bit hoặc 2048-bit, nhờ đó đạt hiệu năng, băng thông và hiệu suất năng lượng gần như không đối thủ. Nhưng độ rộng bus cực lớn này cũng chiếm rất nhiều diện tích chip quý giá, không chỉ hạn chế số lượng chip xếp chồng và dung lượng đóng gói, mà còn tiếp tục kìm hãm hiệu năng của từng card tăng tốc AI đơn lẻ cũng như tổng sức mạnh tính toán của cả cụm hệ thống.

Tuy vậy, JEDEC chưa công bố rõ ràng liệu điều này có đạt được bằng cách tăng tốc độ truyền dữ liệu lên gấp 4 lần (32 GT/s) hay thông qua một cơ chế mã hóa mới với tần số cao hơn.

Bên trong gói SPHBM4 sử dụng die nền tiêu chuẩn của ngành cùng die HBM4, qua đó đảm bảo dung lượng của mỗi khối xếp chồng ngang bằng HBM4 hoặc HBM4E, tối đa có thể đạt 64 GB. Thiết kế này cũng giúp đơn giản hóa bộ điều khiển, cấu trúc đóng gói tổng thể và giảm chi phí.

Về mặt lý thuyết, dung lượng của SPHBM4 thậm chí còn có thể cao hơn, gấp bốn lần HBM4. Điều này khiến nhiều người liên tưởng đến thời kỳ HBM từng được dùng làm bộ nhớ đồ họa, và đặt câu hỏi liệu SPHBM4 có thể trở thành chuẩn VRAM mới hay không.

Câu trả lời rõ ràng là không.

Nguyên nhân là vì mục tiêu thiết kế cốt lõi của SPHBM4 là đạt băng thông cấp HBM4, đảm bảo hiệu năng và dung lượng, chứ không phải tối ưu chi phí và điện năng tiêu thụ.

Chi phí của SPHBM4 chắc chắn thấp hơn HBM4 và HBM4E, đặc biệt nhờ không cần sử dụng interposer đắt đỏ, nhưng bản thân nó vẫn là thiết kế bộ nhớ xếp chồng, nên tất yếu đắt hơn nhiều so với chip DRAM thông thường.

Bên cạnh đó, SPHBM4 còn yêu cầu giao diện nền mạch chuyên dụng, công nghệ TSV (lỗ xuyên silicon) và các kỹ thuật đóng gói tích hợp tiên tiến, khiến chi phí khó có thể hạ xuống mức của GDDR.

Vì vậy, trong card đồ họa, việc dùng một chip SPHBM4 để thay thế nhiều chip GDDR6/7 không những tốn kém hơn, mà mức cải thiện hiệu năng mang lại cũng không thực sự đáng kể.

BÀI MỚI ĐANG THẢO LUẬN